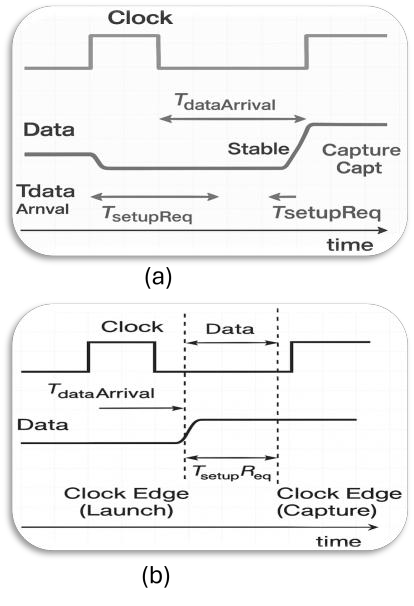

This paper presents an in-depth analysis of timing closure challenges and constraints in Field Programmable Gate Arrays (FPGAs) and Application Specific Integrated Circuits (ASICs). We examine core timing principles, architectural distinctions, and design methodologies influencing timing behavior in both technologies. A case study comparing the Xilinx Kintex UltraScale+ FPGA (XCKU040) with a 7nm ASIC highlights practical timing analysis and performance trade-offs. Experimental results show ASICs achieve superior timing of 45ps setup and 35ps hold, while modern FPGAs remain competitive with 180ps setup and 120ps hold times, validating their suitability for high-performance designs.

翻译:暂无翻译

相关内容

专知会员服务

34+阅读 · 2019年10月18日

专知会员服务

36+阅读 · 2019年10月17日

Arxiv

11+阅读 · 2023年8月31日

Arxiv

21+阅读 · 2023年5月22日

Arxiv

17+阅读 · 2022年11月2日

UniViLM: A Unified Video and Language Pre-Training Model for Multimodal Understanding and Generation

Arxiv

19+阅读 · 2020年2月15日